1. ਜਾਣ-ਪਛਾਣ

ਰੇਡੀਓ ਫ੍ਰੀਕੁਐਂਸੀ (RF) ਊਰਜਾ ਹਾਰਵੈਸਟਿੰਗ (RFEH) ਅਤੇ ਰੇਡੀਏਟਿਵ ਵਾਇਰਲੈੱਸ ਪਾਵਰ ਟ੍ਰਾਂਸਫਰ (WPT) ਨੇ ਬੈਟਰੀ-ਮੁਕਤ ਟਿਕਾਊ ਵਾਇਰਲੈੱਸ ਨੈੱਟਵਰਕ ਪ੍ਰਾਪਤ ਕਰਨ ਦੇ ਤਰੀਕਿਆਂ ਵਜੋਂ ਬਹੁਤ ਦਿਲਚਸਪੀ ਖਿੱਚੀ ਹੈ। ਰੈਕਟੇਨਾ WPT ਅਤੇ RFEH ਸਿਸਟਮਾਂ ਦਾ ਅਧਾਰ ਹਨ ਅਤੇ ਲੋਡ ਨੂੰ ਦਿੱਤੀ ਜਾਣ ਵਾਲੀ DC ਪਾਵਰ 'ਤੇ ਮਹੱਤਵਪੂਰਨ ਪ੍ਰਭਾਵ ਪਾਉਂਦੇ ਹਨ। ਰੈਕਟੇਨਾ ਦੇ ਐਂਟੀਨਾ ਤੱਤ ਸਿੱਧੇ ਤੌਰ 'ਤੇ ਵਾਢੀ ਕੁਸ਼ਲਤਾ ਨੂੰ ਪ੍ਰਭਾਵਤ ਕਰਦੇ ਹਨ, ਜੋ ਕਿ ਕਈ ਕ੍ਰਮਾਂ ਦੇ ਮਾਪ ਦੁਆਰਾ ਕਟਾਈ ਸ਼ਕਤੀ ਨੂੰ ਬਦਲ ਸਕਦੇ ਹਨ। ਇਹ ਪੇਪਰ WPT ਅਤੇ ਅੰਬੀਨਟ RFEH ਐਪਲੀਕੇਸ਼ਨਾਂ ਵਿੱਚ ਵਰਤੇ ਗਏ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨਾਂ ਦੀ ਸਮੀਖਿਆ ਕਰਦਾ ਹੈ। ਰਿਪੋਰਟ ਕੀਤੇ ਗਏ ਰੈਕਟੇਨਾ ਨੂੰ ਦੋ ਮੁੱਖ ਮਾਪਦੰਡਾਂ ਅਨੁਸਾਰ ਸ਼੍ਰੇਣੀਬੱਧ ਕੀਤਾ ਗਿਆ ਹੈ: ਐਂਟੀਨਾ ਸੁਧਾਰ ਕਰਨ ਵਾਲੀ ਪ੍ਰਤੀਰੋਧ ਬੈਂਡਵਿਡਥ ਅਤੇ ਐਂਟੀਨਾ ਦੀਆਂ ਰੇਡੀਏਸ਼ਨ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ। ਹਰੇਕ ਮਾਪਦੰਡ ਲਈ, ਵੱਖ-ਵੱਖ ਐਪਲੀਕੇਸ਼ਨਾਂ ਲਈ ਯੋਗਤਾ ਦਾ ਅੰਕੜਾ (FoM) ਨਿਰਧਾਰਤ ਕੀਤਾ ਜਾਂਦਾ ਹੈ ਅਤੇ ਤੁਲਨਾਤਮਕ ਤੌਰ 'ਤੇ ਸਮੀਖਿਆ ਕੀਤੀ ਜਾਂਦੀ ਹੈ।

WPT ਨੂੰ 20ਵੀਂ ਸਦੀ ਦੇ ਸ਼ੁਰੂ ਵਿੱਚ ਟੇਸਲਾ ਦੁਆਰਾ ਹਜ਼ਾਰਾਂ ਹਾਰਸਪਾਵਰ ਸੰਚਾਰਿਤ ਕਰਨ ਦੇ ਇੱਕ ਢੰਗ ਵਜੋਂ ਪ੍ਰਸਤਾਵਿਤ ਕੀਤਾ ਗਿਆ ਸੀ। ਸ਼ਬਦ "ਰੈਕਟੇਨਾ", ਜੋ ਕਿ RF ਪਾਵਰ ਇਕੱਠਾ ਕਰਨ ਲਈ ਇੱਕ ਰੀਕਟੀਫਾਇਰ ਨਾਲ ਜੁੜੇ ਇੱਕ ਐਂਟੀਨਾ ਦਾ ਵਰਣਨ ਕਰਦਾ ਹੈ, 1950 ਦੇ ਦਹਾਕੇ ਵਿੱਚ ਸਪੇਸ ਮਾਈਕ੍ਰੋਵੇਵ ਪਾਵਰ ਟ੍ਰਾਂਸਮਿਸ਼ਨ ਐਪਲੀਕੇਸ਼ਨਾਂ ਅਤੇ ਆਟੋਨੋਮਸ ਡਰੋਨਾਂ ਨੂੰ ਪਾਵਰ ਦੇਣ ਲਈ ਉਭਰਿਆ। ਸਰਵ-ਦਿਸ਼ਾਵੀ, ਲੰਬੀ-ਸੀਮਾ WPT ਪ੍ਰਸਾਰ ਮਾਧਿਅਮ (ਹਵਾ) ਦੇ ਭੌਤਿਕ ਗੁਣਾਂ ਦੁਆਰਾ ਸੀਮਤ ਹੈ। ਇਸ ਲਈ, ਵਪਾਰਕ WPT ਮੁੱਖ ਤੌਰ 'ਤੇ ਵਾਇਰਲੈੱਸ ਖਪਤਕਾਰ ਇਲੈਕਟ੍ਰਾਨਿਕਸ ਚਾਰਜਿੰਗ ਜਾਂ RFID ਲਈ ਨੇੜੇ-ਖੇਤਰ ਗੈਰ-ਰੇਡੀਏਟਿਵ ਪਾਵਰ ਟ੍ਰਾਂਸਫਰ ਤੱਕ ਸੀਮਿਤ ਹੈ।

ਜਿਵੇਂ-ਜਿਵੇਂ ਸੈਮੀਕੰਡਕਟਰ ਡਿਵਾਈਸਾਂ ਅਤੇ ਵਾਇਰਲੈੱਸ ਸੈਂਸਰ ਨੋਡਾਂ ਦੀ ਬਿਜਲੀ ਦੀ ਖਪਤ ਘਟਦੀ ਰਹਿੰਦੀ ਹੈ, ਅੰਬੀਨਟ RFEH ਜਾਂ ਵੰਡੇ ਗਏ ਘੱਟ-ਪਾਵਰ ਸਰਵ-ਦਿਸ਼ਾਵੀ ਟ੍ਰਾਂਸਮੀਟਰਾਂ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਸੈਂਸਰ ਨੋਡਾਂ ਨੂੰ ਪਾਵਰ ਦੇਣਾ ਵਧੇਰੇ ਸੰਭਵ ਹੋ ਜਾਂਦਾ ਹੈ। ਅਲਟਰਾ-ਲੋ-ਪਾਵਰ ਵਾਇਰਲੈੱਸ ਪਾਵਰ ਸਿਸਟਮ ਵਿੱਚ ਆਮ ਤੌਰ 'ਤੇ ਇੱਕ RF ਪ੍ਰਾਪਤੀ ਫਰੰਟ ਐਂਡ, DC ਪਾਵਰ ਅਤੇ ਮੈਮੋਰੀ ਪ੍ਰਬੰਧਨ, ਅਤੇ ਇੱਕ ਘੱਟ-ਪਾਵਰ ਮਾਈਕ੍ਰੋਪ੍ਰੋਸੈਸਰ ਅਤੇ ਟ੍ਰਾਂਸਸੀਵਰ ਹੁੰਦੇ ਹਨ।

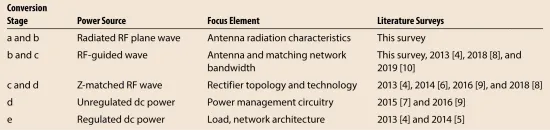

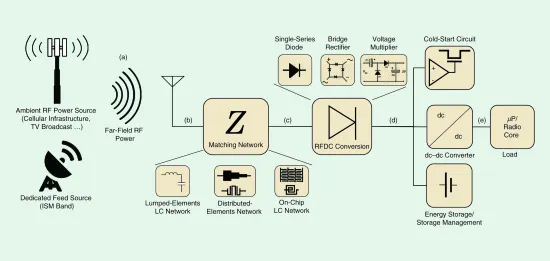

ਚਿੱਤਰ 1 ਇੱਕ RFEH ਵਾਇਰਲੈੱਸ ਨੋਡ ਦੇ ਆਰਕੀਟੈਕਚਰ ਅਤੇ ਆਮ ਤੌਰ 'ਤੇ ਰਿਪੋਰਟ ਕੀਤੇ ਗਏ RF ਫਰੰਟ-ਐਂਡ ਲਾਗੂਕਰਨਾਂ ਨੂੰ ਦਰਸਾਉਂਦਾ ਹੈ। ਵਾਇਰਲੈੱਸ ਪਾਵਰ ਸਿਸਟਮ ਦੀ ਐਂਡ-ਟੂ-ਐਂਡ ਕੁਸ਼ਲਤਾ ਅਤੇ ਸਿੰਕ੍ਰੋਨਾਈਜ਼ਡ ਵਾਇਰਲੈੱਸ ਜਾਣਕਾਰੀ ਅਤੇ ਪਾਵਰ ਟ੍ਰਾਂਸਫਰ ਨੈੱਟਵਰਕ ਦੀ ਆਰਕੀਟੈਕਚਰ ਵਿਅਕਤੀਗਤ ਹਿੱਸਿਆਂ, ਜਿਵੇਂ ਕਿ ਐਂਟੀਨਾ, ਰੀਕਟੀਫਾਇਰ ਅਤੇ ਪਾਵਰ ਮੈਨੇਜਮੈਂਟ ਸਰਕਟਾਂ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ 'ਤੇ ਨਿਰਭਰ ਕਰਦੀ ਹੈ। ਸਿਸਟਮ ਦੇ ਵੱਖ-ਵੱਖ ਹਿੱਸਿਆਂ ਲਈ ਕਈ ਸਾਹਿਤ ਸਰਵੇਖਣ ਕੀਤੇ ਗਏ ਹਨ। ਸਾਰਣੀ 1 ਪਾਵਰ ਪਰਿਵਰਤਨ ਪੜਾਅ, ਕੁਸ਼ਲ ਪਾਵਰ ਪਰਿਵਰਤਨ ਲਈ ਮੁੱਖ ਭਾਗਾਂ ਅਤੇ ਹਰੇਕ ਹਿੱਸੇ ਲਈ ਸੰਬੰਧਿਤ ਸਾਹਿਤ ਸਰਵੇਖਣਾਂ ਦਾ ਸਾਰ ਦਿੰਦੀ ਹੈ। ਹਾਲੀਆ ਸਾਹਿਤ ਪਾਵਰ ਪਰਿਵਰਤਨ ਤਕਨਾਲੋਜੀ, ਰੀਕਟੀਫਾਇਰ ਟੋਪੋਲੋਜੀ, ਜਾਂ ਨੈੱਟਵਰਕ-ਜਾਗਰੂਕ RFEH 'ਤੇ ਕੇਂਦ੍ਰਤ ਕਰਦਾ ਹੈ।

ਚਿੱਤਰ 1

ਹਾਲਾਂਕਿ, RFEH ਵਿੱਚ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨ ਨੂੰ ਇੱਕ ਮਹੱਤਵਪੂਰਨ ਹਿੱਸਾ ਨਹੀਂ ਮੰਨਿਆ ਜਾਂਦਾ ਹੈ। ਹਾਲਾਂਕਿ ਕੁਝ ਸਾਹਿਤ ਐਂਟੀਨਾ ਬੈਂਡਵਿਡਥ ਅਤੇ ਕੁਸ਼ਲਤਾ ਨੂੰ ਸਮੁੱਚੇ ਦ੍ਰਿਸ਼ਟੀਕੋਣ ਤੋਂ ਜਾਂ ਇੱਕ ਖਾਸ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨ ਦ੍ਰਿਸ਼ਟੀਕੋਣ ਤੋਂ ਵਿਚਾਰਦੇ ਹਨ, ਜਿਵੇਂ ਕਿ ਛੋਟੇ ਜਾਂ ਪਹਿਨਣਯੋਗ ਐਂਟੀਨਾ, ਪਾਵਰ ਰਿਸੈਪਸ਼ਨ ਅਤੇ ਪਰਿਵਰਤਨ ਕੁਸ਼ਲਤਾ 'ਤੇ ਕੁਝ ਐਂਟੀਨਾ ਪੈਰਾਮੀਟਰਾਂ ਦੇ ਪ੍ਰਭਾਵ ਦਾ ਵਿਸਥਾਰ ਵਿੱਚ ਵਿਸ਼ਲੇਸ਼ਣ ਨਹੀਂ ਕੀਤਾ ਗਿਆ ਹੈ।

ਇਹ ਪੇਪਰ ਮਿਆਰੀ ਸੰਚਾਰ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨ ਤੋਂ RFEH ਅਤੇ WPT ਖਾਸ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨ ਚੁਣੌਤੀਆਂ ਨੂੰ ਵੱਖਰਾ ਕਰਨ ਦੇ ਟੀਚੇ ਨਾਲ ਰੈਕਟੇਨਾ ਵਿੱਚ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨ ਤਕਨੀਕਾਂ ਦੀ ਸਮੀਖਿਆ ਕਰਦਾ ਹੈ। ਐਂਟੀਨਾ ਦੀ ਤੁਲਨਾ ਦੋ ਦ੍ਰਿਸ਼ਟੀਕੋਣਾਂ ਤੋਂ ਕੀਤੀ ਜਾਂਦੀ ਹੈ: ਐਂਡ-ਟੂ-ਐਂਡ ਇਮਪੀਡੈਂਸ ਮੈਚਿੰਗ ਅਤੇ ਰੇਡੀਏਸ਼ਨ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ; ਹਰੇਕ ਮਾਮਲੇ ਵਿੱਚ, FoM ਦੀ ਪਛਾਣ ਕੀਤੀ ਜਾਂਦੀ ਹੈ ਅਤੇ ਅਤਿ-ਆਧੁਨਿਕ (SoA) ਐਂਟੀਨਾ ਵਿੱਚ ਸਮੀਖਿਆ ਕੀਤੀ ਜਾਂਦੀ ਹੈ।

2. ਬੈਂਡਵਿਡਥ ਅਤੇ ਮੈਚਿੰਗ: ਗੈਰ-50Ω RF ਨੈੱਟਵਰਕ

50Ω ਦੀ ਵਿਸ਼ੇਸ਼ਤਾ ਵਾਲੀ ਰੁਕਾਵਟ ਮਾਈਕ੍ਰੋਵੇਵ ਇੰਜੀਨੀਅਰਿੰਗ ਐਪਲੀਕੇਸ਼ਨਾਂ ਵਿੱਚ ਐਟੇਨਿਊਏਸ਼ਨ ਅਤੇ ਪਾਵਰ ਵਿਚਕਾਰ ਸਮਝੌਤੇ ਦਾ ਇੱਕ ਸ਼ੁਰੂਆਤੀ ਵਿਚਾਰ ਹੈ। ਐਂਟੀਨਾ ਵਿੱਚ, ਰੁਕਾਵਟ ਬੈਂਡਵਿਡਥ ਨੂੰ ਫ੍ਰੀਕੁਐਂਸੀ ਰੇਂਜ ਵਜੋਂ ਪਰਿਭਾਸ਼ਿਤ ਕੀਤਾ ਜਾਂਦਾ ਹੈ ਜਿੱਥੇ ਪ੍ਰਤੀਬਿੰਬਿਤ ਸ਼ਕਤੀ 10% (S11< − 10 dB) ਤੋਂ ਘੱਟ ਹੁੰਦੀ ਹੈ। ਕਿਉਂਕਿ ਘੱਟ ਸ਼ੋਰ ਐਂਪਲੀਫਾਇਰ (LNAs), ਪਾਵਰ ਐਂਪਲੀਫਾਇਰ, ਅਤੇ ਡਿਟੈਕਟਰ ਆਮ ਤੌਰ 'ਤੇ 50Ω ਇਨਪੁੱਟ ਇੰਪਲੀਫਾਇਰ ਮੈਚ ਨਾਲ ਡਿਜ਼ਾਈਨ ਕੀਤੇ ਜਾਂਦੇ ਹਨ, ਇੱਕ 50Ω ਸਰੋਤ ਨੂੰ ਰਵਾਇਤੀ ਤੌਰ 'ਤੇ ਹਵਾਲਾ ਦਿੱਤਾ ਜਾਂਦਾ ਹੈ।

ਇੱਕ ਰੈਕਟੇਨਾ ਵਿੱਚ, ਐਂਟੀਨਾ ਦਾ ਆਉਟਪੁੱਟ ਸਿੱਧਾ ਰੀਕਟੀਫਾਇਰ ਵਿੱਚ ਫੀਡ ਕੀਤਾ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਡਾਇਓਡ ਦੀ ਗੈਰ-ਰੇਖਿਕਤਾ ਇਨਪੁਟ ਇਮਪੀਡੈਂਸ ਵਿੱਚ ਇੱਕ ਵੱਡੀ ਭਿੰਨਤਾ ਦਾ ਕਾਰਨ ਬਣਦੀ ਹੈ, ਜਿਸ ਵਿੱਚ ਕੈਪੇਸਿਟਿਵ ਕੰਪੋਨੈਂਟ ਹਾਵੀ ਹੁੰਦਾ ਹੈ। 50Ω ਐਂਟੀਨਾ ਮੰਨ ਕੇ, ਮੁੱਖ ਚੁਣੌਤੀ ਇੱਕ ਵਾਧੂ RF ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਡਿਜ਼ਾਈਨ ਕਰਨਾ ਹੈ ਤਾਂ ਜੋ ਇਨਪੁਟ ਇਮਪੀਡੈਂਸ ਨੂੰ ਦਿਲਚਸਪੀ ਦੀ ਬਾਰੰਬਾਰਤਾ 'ਤੇ ਰੀਕਟੀਫਾਇਰ ਦੇ ਇਮਪੀਡੈਂਸ ਵਿੱਚ ਬਦਲਿਆ ਜਾ ਸਕੇ ਅਤੇ ਇਸਨੂੰ ਇੱਕ ਖਾਸ ਪਾਵਰ ਪੱਧਰ ਲਈ ਅਨੁਕੂਲ ਬਣਾਇਆ ਜਾ ਸਕੇ। ਇਸ ਸਥਿਤੀ ਵਿੱਚ, ਕੁਸ਼ਲ RF ਤੋਂ DC ਪਰਿਵਰਤਨ ਨੂੰ ਯਕੀਨੀ ਬਣਾਉਣ ਲਈ ਐਂਡ-ਟੂ-ਐਂਡ ਇਮਪੀਡੈਂਸ ਬੈਂਡਵਿਡਥ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ। ਇਸ ਲਈ, ਹਾਲਾਂਕਿ ਐਂਟੀਨਾ ਸਿਧਾਂਤਕ ਤੌਰ 'ਤੇ ਅਨੰਤ ਜਾਂ ਅਲਟਰਾ-ਵਾਈਡ ਬੈਂਡਵਿਡਥ ਨੂੰ ਪੀਰੀਅਡਿਕ ਐਲੀਮੈਂਟਸ ਜਾਂ ਸਵੈ-ਪੂਰਕ ਜਿਓਮੈਟਰੀ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਪ੍ਰਾਪਤ ਕਰ ਸਕਦੇ ਹਨ, ਰੈਕਟੇਨਾ ਦੀ ਬੈਂਡਵਿਡਥ ਰੀਕਟੀਫਾਇਰ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਦੁਆਰਾ ਰੁਕਾਵਟ ਬਣ ਜਾਵੇਗੀ।

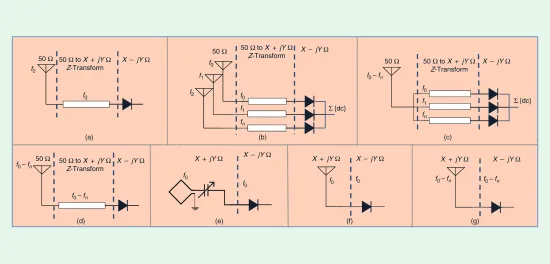

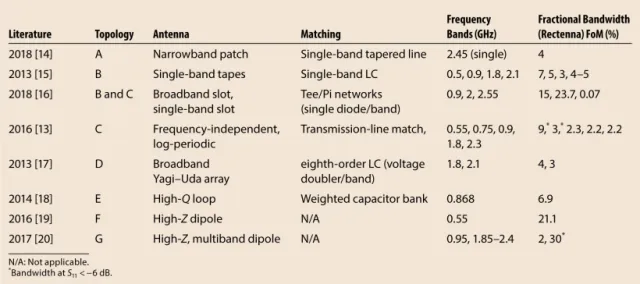

ਐਂਟੀਨਾ ਅਤੇ ਰੀਕਟੀਫਾਇਰ ਵਿਚਕਾਰ ਪ੍ਰਤੀਬਿੰਬਾਂ ਨੂੰ ਘੱਟ ਤੋਂ ਘੱਟ ਕਰਕੇ ਅਤੇ ਪਾਵਰ ਟ੍ਰਾਂਸਫਰ ਨੂੰ ਵੱਧ ਤੋਂ ਵੱਧ ਕਰਕੇ ਸਿੰਗਲ-ਬੈਂਡ ਅਤੇ ਮਲਟੀ-ਬੈਂਡ ਹਾਰਵੈਸਟਿੰਗ ਜਾਂ WPT ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਕਈ ਰੈਕਟੇਨਾ ਟੌਪੋਲੋਜੀ ਪ੍ਰਸਤਾਵਿਤ ਕੀਤੀਆਂ ਗਈਆਂ ਹਨ। ਚਿੱਤਰ 2 ਰਿਪੋਰਟ ਕੀਤੇ ਗਏ ਰੈਕਟੇਨਾ ਟੌਪੋਲੋਜੀ ਦੇ ਢਾਂਚੇ ਨੂੰ ਦਰਸਾਉਂਦਾ ਹੈ, ਜੋ ਉਹਨਾਂ ਦੇ ਇਮਪੀਡੈਂਸ ਮੈਚਿੰਗ ਆਰਕੀਟੈਕਚਰ ਦੁਆਰਾ ਸ਼੍ਰੇਣੀਬੱਧ ਕੀਤੇ ਗਏ ਹਨ। ਸਾਰਣੀ 2 ਹਰੇਕ ਸ਼੍ਰੇਣੀ ਲਈ ਐਂਡ-ਟੂ-ਐਂਡ ਬੈਂਡਵਿਡਥ (ਇਸ ਮਾਮਲੇ ਵਿੱਚ, FoM) ਦੇ ਸੰਬੰਧ ਵਿੱਚ ਉੱਚ-ਪ੍ਰਦਰਸ਼ਨ ਵਾਲੇ ਰੈਕਟੇਨਾ ਦੀਆਂ ਉਦਾਹਰਣਾਂ ਦਿਖਾਉਂਦਾ ਹੈ।

ਚਿੱਤਰ 2 ਬੈਂਡਵਿਡਥ ਅਤੇ ਇਮਪੀਡੈਂਸ ਮੈਚਿੰਗ ਦੇ ਦ੍ਰਿਸ਼ਟੀਕੋਣ ਤੋਂ ਰੈਕਟੇਨਾ ਟੌਪੋਲੋਜੀਜ਼। (a) ਸਟੈਂਡਰਡ ਐਂਟੀਨਾ ਵਾਲਾ ਸਿੰਗਲ-ਬੈਂਡ ਰੈਕਟੇਨਾ। (b) ਮਲਟੀਬੈਂਡ ਰੈਕਟੇਨਾ (ਕਈ ਆਪਸੀ ਤੌਰ 'ਤੇ ਜੁੜੇ ਐਂਟੀਨਾ ਤੋਂ ਬਣਿਆ) ਪ੍ਰਤੀ ਬੈਂਡ ਇੱਕ ਰੀਕਟੀਫਾਇਰ ਅਤੇ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਦੇ ਨਾਲ। (c) ਮਲਟੀਪਲ RF ਪੋਰਟਾਂ ਵਾਲਾ ਬ੍ਰੌਡਬੈਂਡ ਰੈਕਟੇਨਾ ਅਤੇ ਹਰੇਕ ਬੈਂਡ ਲਈ ਵੱਖਰੇ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ। (d) ਬ੍ਰੌਡਬੈਂਡ ਐਂਟੀਨਾ ਅਤੇ ਬ੍ਰੌਡਬੈਂਡ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਵਾਲਾ ਬ੍ਰੌਡਬੈਂਡ ਰੈਕਟੇਨਾ। (e) ਸਿੰਗਲ-ਬੈਂਡ ਰੈਕਟੇਨਾ ਜੋ ਸਿੱਧੇ ਤੌਰ 'ਤੇ ਰੀਕਟੀਫਾਇਰ ਨਾਲ ਮੇਲ ਖਾਂਦਾ ਇਲੈਕਟ੍ਰਿਕ ਤੌਰ 'ਤੇ ਛੋਟਾ ਐਂਟੀਨਾ ਵਰਤਦਾ ਹੈ। (f) ਸਿੰਗਲ-ਬੈਂਡ, ਇਲੈਕਟ੍ਰਿਕ ਤੌਰ 'ਤੇ ਵੱਡਾ ਐਂਟੀਨਾ ਜਿਸ ਵਿੱਚ ਰੀਕਟੀਫਾਇਰ ਨਾਲ ਜੋੜਨ ਲਈ ਗੁੰਝਲਦਾਰ ਇਮਪੀਡੈਂਸ ਹੈ। (g) ਫ੍ਰੀਕੁਐਂਸੀ ਦੀ ਇੱਕ ਰੇਂਜ ਉੱਤੇ ਰੀਕਟੀਫਾਇਰ ਨਾਲ ਜੋੜਨ ਲਈ ਗੁੰਝਲਦਾਰ ਇਮਪੀਡੈਂਸ ਵਾਲਾ ਬ੍ਰੌਡਬੈਂਡ ਰੈਕਟੇਨਾ।

ਜਦੋਂ ਕਿ ਸਮਰਪਿਤ ਫੀਡ ਤੋਂ WPT ਅਤੇ ਅੰਬੀਨਟ RFEH ਵੱਖ-ਵੱਖ ਰੈਕਟੇਨਾ ਐਪਲੀਕੇਸ਼ਨ ਹਨ, ਬੈਂਡਵਿਡਥ ਦ੍ਰਿਸ਼ਟੀਕੋਣ ਤੋਂ ਉੱਚ ਪਾਵਰ ਪਰਿਵਰਤਨ ਕੁਸ਼ਲਤਾ (PCE) ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਐਂਟੀਨਾ, ਰੀਕਟੀਫਾਇਰ ਅਤੇ ਲੋਡ ਵਿਚਕਾਰ ਐਂਡ-ਟੂ-ਐਂਡ ਮੈਚਿੰਗ ਪ੍ਰਾਪਤ ਕਰਨਾ ਬੁਨਿਆਦੀ ਹੈ। ਫਿਰ ਵੀ, WPT ਰੈਕਟੇਨਾ ਕੁਝ ਪਾਵਰ ਪੱਧਰਾਂ (ਟੌਪੋਲੋਜੀਜ਼ a, e ਅਤੇ f) 'ਤੇ ਸਿੰਗਲ-ਬੈਂਡ PCE ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਣ ਲਈ ਉੱਚ ਗੁਣਵੱਤਾ ਵਾਲੇ ਫੈਕਟਰ ਮੈਚਿੰਗ (ਘੱਟ S11) ਪ੍ਰਾਪਤ ਕਰਨ 'ਤੇ ਵਧੇਰੇ ਧਿਆਨ ਕੇਂਦ੍ਰਤ ਕਰਦੇ ਹਨ। ਸਿੰਗਲ-ਬੈਂਡ WPT ਦੀ ਵਿਸ਼ਾਲ ਬੈਂਡਵਿਡਥ ਡੀਟਿਊਨਿੰਗ, ਨਿਰਮਾਣ ਨੁਕਸ ਅਤੇ ਪੈਕੇਜਿੰਗ ਪਰਜੀਵੀਆਂ ਪ੍ਰਤੀ ਸਿਸਟਮ ਪ੍ਰਤੀਰੋਧਕ ਸ਼ਕਤੀ ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਂਦੀ ਹੈ। ਦੂਜੇ ਪਾਸੇ, RFEH ਰੈਕਟੇਨਾ ਮਲਟੀ-ਬੈਂਡ ਓਪਰੇਸ਼ਨ ਨੂੰ ਤਰਜੀਹ ਦਿੰਦੇ ਹਨ ਅਤੇ ਟੋਪੋਲੋਜੀਜ਼ bd ਅਤੇ g ਨਾਲ ਸਬੰਧਤ ਹਨ, ਕਿਉਂਕਿ ਇੱਕ ਸਿੰਗਲ ਬੈਂਡ ਦੀ ਪਾਵਰ ਸਪੈਕਟ੍ਰਲ ਘਣਤਾ (PSD) ਆਮ ਤੌਰ 'ਤੇ ਘੱਟ ਹੁੰਦੀ ਹੈ।

3. ਆਇਤਾਕਾਰ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨ

1. ਸਿੰਗਲ-ਫ੍ਰੀਕੁਐਂਸੀ ਰੈਕਟੇਨਾ

ਸਿੰਗਲ-ਫ੍ਰੀਕੁਐਂਸੀ ਰੈਕਟੇਨਾ (ਟੌਪੋਲੋਜੀ ਏ) ਦਾ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨ ਮੁੱਖ ਤੌਰ 'ਤੇ ਸਟੈਂਡਰਡ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨ 'ਤੇ ਅਧਾਰਤ ਹੈ, ਜਿਵੇਂ ਕਿ ਲੀਨੀਅਰ ਪੋਲਰਾਈਜ਼ੇਸ਼ਨ (ਐਲਪੀ) ਜਾਂ ਗੋਲਾਕਾਰ ਪੋਲਰਾਈਜ਼ੇਸ਼ਨ (ਸੀਪੀ) ਰੇਡੀਏਟਿੰਗ ਪੈਚ ਜ਼ਮੀਨੀ ਜਹਾਜ਼ 'ਤੇ, ਡਾਇਪੋਲ ਐਂਟੀਨਾ ਅਤੇ ਇਨਵਰਟੇਡ ਐਫ ਐਂਟੀਨਾ। ਡਿਫਰੈਂਸ਼ੀਅਲ ਬੈਂਡ ਰੈਕਟੇਨਾ ਡੀਸੀ ਸੁਮੇਲ ਐਰੇ 'ਤੇ ਅਧਾਰਤ ਹੈ ਜੋ ਮਲਟੀਪਲ ਐਂਟੀਨਾ ਯੂਨਿਟਾਂ ਜਾਂ ਮਿਸ਼ਰਤ ਡੀਸੀ ਅਤੇ ਆਰਐਫ ਮਲਟੀਪਲ ਪੈਚ ਯੂਨਿਟਾਂ ਦੇ ਸੁਮੇਲ ਨਾਲ ਸੰਰਚਿਤ ਕੀਤਾ ਗਿਆ ਹੈ।

ਕਿਉਂਕਿ ਬਹੁਤ ਸਾਰੇ ਪ੍ਰਸਤਾਵਿਤ ਐਂਟੀਨਾ ਸਿੰਗਲ-ਫ੍ਰੀਕੁਐਂਸੀ ਐਂਟੀਨਾ ਹਨ ਅਤੇ ਸਿੰਗਲ-ਫ੍ਰੀਕੁਐਂਸੀ WPT ਦੀਆਂ ਜ਼ਰੂਰਤਾਂ ਨੂੰ ਪੂਰਾ ਕਰਦੇ ਹਨ, ਇਸ ਲਈ ਜਦੋਂ ਵਾਤਾਵਰਣਕ ਮਲਟੀ-ਫ੍ਰੀਕੁਐਂਸੀ RFEH ਦੀ ਮੰਗ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਤਾਂ ਮਲਟੀਪਲ ਸਿੰਗਲ-ਫ੍ਰੀਕੁਐਂਸੀ ਐਂਟੀਨਾ ਨੂੰ ਮਲਟੀ-ਬੈਂਡ ਰੈਕਟੇਨਾ (ਟੌਪੋਲੋਜੀ B) ਵਿੱਚ ਆਪਸੀ ਕਪਲਿੰਗ ਸਪ੍ਰੈਸ਼ਨ ਅਤੇ ਸੁਤੰਤਰ DC ਸੁਮੇਲ ਨਾਲ ਜੋੜਿਆ ਜਾਂਦਾ ਹੈ ਤਾਂ ਜੋ ਪਾਵਰ ਮੈਨੇਜਮੈਂਟ ਸਰਕਟ ਤੋਂ ਬਾਅਦ ਉਹਨਾਂ ਨੂੰ RF ਪ੍ਰਾਪਤੀ ਅਤੇ ਪਰਿਵਰਤਨ ਸਰਕਟ ਤੋਂ ਪੂਰੀ ਤਰ੍ਹਾਂ ਅਲੱਗ ਕੀਤਾ ਜਾ ਸਕੇ। ਇਸ ਲਈ ਹਰੇਕ ਬੈਂਡ ਲਈ ਕਈ ਪਾਵਰ ਮੈਨੇਜਮੈਂਟ ਸਰਕਟਾਂ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਜੋ ਬੂਸਟ ਕਨਵਰਟਰ ਦੀ ਕੁਸ਼ਲਤਾ ਨੂੰ ਘਟਾ ਸਕਦਾ ਹੈ ਕਿਉਂਕਿ ਇੱਕ ਸਿੰਗਲ ਬੈਂਡ ਦੀ DC ਪਾਵਰ ਘੱਟ ਹੁੰਦੀ ਹੈ।

2. ਮਲਟੀ-ਬੈਂਡ ਅਤੇ ਬ੍ਰਾਡਬੈਂਡ RFEH ਐਂਟੀਨਾ

ਵਾਤਾਵਰਣ ਸੰਬੰਧੀ RFEH ਅਕਸਰ ਮਲਟੀ-ਬੈਂਡ ਪ੍ਰਾਪਤੀ ਨਾਲ ਜੁੜਿਆ ਹੁੰਦਾ ਹੈ; ਇਸ ਲਈ, ਸਟੈਂਡਰਡ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨਾਂ ਦੀ ਬੈਂਡਵਿਡਥ ਅਤੇ ਡੁਅਲ-ਬੈਂਡ ਜਾਂ ਬੈਂਡ ਐਂਟੀਨਾ ਐਰੇ ਬਣਾਉਣ ਦੇ ਤਰੀਕਿਆਂ ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਣ ਲਈ ਕਈ ਤਰ੍ਹਾਂ ਦੀਆਂ ਤਕਨੀਕਾਂ ਦਾ ਪ੍ਰਸਤਾਵ ਦਿੱਤਾ ਗਿਆ ਹੈ। ਇਸ ਭਾਗ ਵਿੱਚ, ਅਸੀਂ RFEHs ਲਈ ਕਸਟਮ ਐਂਟੀਨਾ ਡਿਜ਼ਾਈਨਾਂ ਦੀ ਸਮੀਖਿਆ ਕਰਦੇ ਹਾਂ, ਨਾਲ ਹੀ ਕਲਾਸਿਕ ਮਲਟੀ-ਬੈਂਡ ਐਂਟੀਨਾ ਜਿਨ੍ਹਾਂ ਨੂੰ ਰੈਕਟੇਨਾ ਵਜੋਂ ਵਰਤਿਆ ਜਾ ਸਕਦਾ ਹੈ।

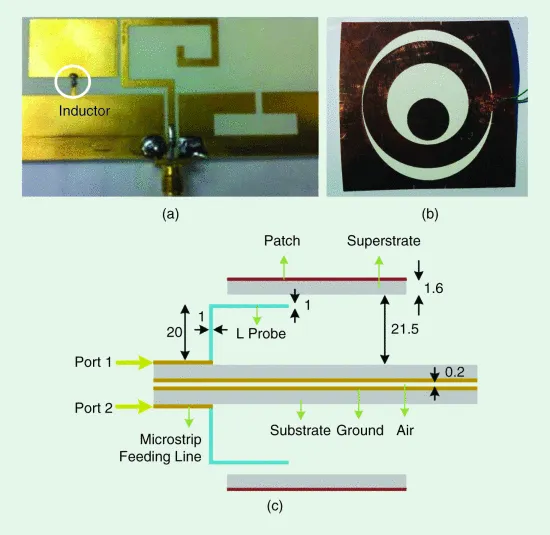

ਕੋਪਲਾਨਰ ਵੇਵਗਾਈਡ (CPW) ਮੋਨੋਪੋਲ ਐਂਟੀਨਾ ਇੱਕੋ ਫ੍ਰੀਕੁਐਂਸੀ 'ਤੇ ਮਾਈਕ੍ਰੋਸਟ੍ਰਿਪ ਪੈਚ ਐਂਟੀਨਾ ਨਾਲੋਂ ਘੱਟ ਖੇਤਰਫਲ 'ਤੇ ਕਬਜ਼ਾ ਕਰਦੇ ਹਨ ਅਤੇ LP ਜਾਂ CP ਤਰੰਗਾਂ ਪੈਦਾ ਕਰਦੇ ਹਨ, ਅਤੇ ਅਕਸਰ ਬ੍ਰੌਡਬੈਂਡ ਵਾਤਾਵਰਣਕ ਰੈਕਟੇਨਾ ਲਈ ਵਰਤੇ ਜਾਂਦੇ ਹਨ। ਰਿਫਲੈਕਸ਼ਨ ਪਲੇਨਾਂ ਦੀ ਵਰਤੋਂ ਆਈਸੋਲੇਸ਼ਨ ਵਧਾਉਣ ਅਤੇ ਲਾਭ ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਣ ਲਈ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਜਿਸਦੇ ਨਤੀਜੇ ਵਜੋਂ ਪੈਚ ਐਂਟੀਨਾ ਦੇ ਸਮਾਨ ਰੇਡੀਏਸ਼ਨ ਪੈਟਰਨ ਬਣਦੇ ਹਨ। ਸਲਾਟਡ ਕੋਪਲਾਨਰ ਵੇਵਗਾਈਡ ਐਂਟੀਨਾ ਦੀ ਵਰਤੋਂ ਮਲਟੀਪਲ ਫ੍ਰੀਕੁਐਂਸੀ ਬੈਂਡਾਂ ਲਈ ਇੰਪੀਡੈਂਸ ਬੈਂਡਵਿਡਥ ਨੂੰ ਬਿਹਤਰ ਬਣਾਉਣ ਲਈ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਜਿਵੇਂ ਕਿ 1.8–2.7 GHz ਜਾਂ 1–3 GHz। ਕਪਲਡ-ਫੈੱਡ ਸਲਾਟ ਐਂਟੀਨਾ ਅਤੇ ਪੈਚ ਐਂਟੀਨਾ ਵੀ ਆਮ ਤੌਰ 'ਤੇ ਮਲਟੀ-ਬੈਂਡ ਰੈਕਟੇਨਾ ਡਿਜ਼ਾਈਨਾਂ ਵਿੱਚ ਵਰਤੇ ਜਾਂਦੇ ਹਨ। ਚਿੱਤਰ 3 ਕੁਝ ਰਿਪੋਰਟ ਕੀਤੇ ਮਲਟੀ-ਬੈਂਡ ਐਂਟੀਨਾ ਦਿਖਾਉਂਦਾ ਹੈ ਜੋ ਇੱਕ ਤੋਂ ਵੱਧ ਬੈਂਡਵਿਡਥ ਸੁਧਾਰ ਤਕਨੀਕ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹਨ।

ਚਿੱਤਰ 3

ਐਂਟੀਨਾ-ਰੈਕਟੀਫਾਇਰ ਇਮਪੀਡੈਂਸ ਮੈਚਿੰਗ

50Ω ਐਂਟੀਨਾ ਨੂੰ ਇੱਕ ਗੈਰ-ਰੇਖਿਕ ਰੀਕਟੀਫਾਇਰ ਨਾਲ ਮਿਲਾਉਣਾ ਚੁਣੌਤੀਪੂਰਨ ਹੈ ਕਿਉਂਕਿ ਇਸਦਾ ਇਨਪੁਟ ਇਮਪੀਡੈਂਸ ਬਾਰੰਬਾਰਤਾ ਦੇ ਨਾਲ ਬਹੁਤ ਬਦਲਦਾ ਹੈ। ਟੌਪੋਲੋਜੀਜ਼ A ਅਤੇ B (ਚਿੱਤਰ 2) ਵਿੱਚ, ਆਮ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਇੱਕ LC ਮੈਚ ਹੈ ਜੋ ਲੁੰਪਡ ਐਲੀਮੈਂਟਸ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ; ਹਾਲਾਂਕਿ, ਸਾਪੇਖਿਕ ਬੈਂਡਵਿਡਥ ਆਮ ਤੌਰ 'ਤੇ ਜ਼ਿਆਦਾਤਰ ਸੰਚਾਰ ਬੈਂਡਾਂ ਨਾਲੋਂ ਘੱਟ ਹੁੰਦੀ ਹੈ। ਸਿੰਗਲ-ਬੈਂਡ ਸਟੱਬ ਮੈਚਿੰਗ ਆਮ ਤੌਰ 'ਤੇ 6 GHz ਤੋਂ ਘੱਟ ਮਾਈਕ੍ਰੋਵੇਵ ਅਤੇ ਮਿਲੀਮੀਟਰ-ਵੇਵ ਬੈਂਡਾਂ ਵਿੱਚ ਵਰਤੀ ਜਾਂਦੀ ਹੈ, ਅਤੇ ਰਿਪੋਰਟ ਕੀਤੇ ਗਏ ਮਿਲੀਮੀਟਰ-ਵੇਵ ਰੈਕਟੇਨਾ ਵਿੱਚ ਇੱਕ ਅੰਦਰੂਨੀ ਤੌਰ 'ਤੇ ਤੰਗ ਬੈਂਡਵਿਡਥ ਹੁੰਦੀ ਹੈ ਕਿਉਂਕਿ ਉਹਨਾਂ ਦੀ PCE ਬੈਂਡਵਿਡਥ ਆਉਟਪੁੱਟ ਹਾਰਮੋਨਿਕ ਦਮਨ ਦੁਆਰਾ ਰੁਕਾਵਟ ਹੁੰਦੀ ਹੈ, ਜੋ ਉਹਨਾਂ ਨੂੰ 24 GHz ਗੈਰ-ਲਾਇਸੈਂਸ ਵਾਲੇ ਬੈਂਡ ਵਿੱਚ ਸਿੰਗਲ-ਬੈਂਡ WPT ਐਪਲੀਕੇਸ਼ਨਾਂ ਲਈ ਖਾਸ ਤੌਰ 'ਤੇ ਢੁਕਵਾਂ ਬਣਾਉਂਦੀ ਹੈ।

ਟੋਪੋਲੋਜੀ C ਅਤੇ D ਵਿੱਚ ਰੈਕਟੇਨਾ ਵਿੱਚ ਵਧੇਰੇ ਗੁੰਝਲਦਾਰ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਹੁੰਦੇ ਹਨ। ਬ੍ਰੌਡਬੈਂਡ ਮੈਚਿੰਗ ਲਈ ਪੂਰੀ ਤਰ੍ਹਾਂ ਵੰਡੀਆਂ ਗਈਆਂ ਲਾਈਨ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕਾਂ ਦਾ ਪ੍ਰਸਤਾਵ ਰੱਖਿਆ ਗਿਆ ਹੈ, ਜਿਸ ਵਿੱਚ ਆਉਟਪੁੱਟ ਪੋਰਟ 'ਤੇ ਇੱਕ RF ਬਲਾਕ/DC ਸ਼ਾਰਟ ਸਰਕਟ (ਪਾਸ ਫਿਲਟਰ) ਜਾਂ ਡਾਇਓਡ ਹਾਰਮੋਨਿਕਸ ਲਈ ਵਾਪਸੀ ਮਾਰਗ ਵਜੋਂ ਇੱਕ DC ਬਲਾਕਿੰਗ ਕੈਪੇਸੀਟਰ ਹੁੰਦਾ ਹੈ। ਰੀਕਟੀਫਾਇਰ ਕੰਪੋਨੈਂਟਸ ਨੂੰ ਪ੍ਰਿੰਟਿਡ ਸਰਕਟ ਬੋਰਡ (PCB) ਇੰਟਰਡਿਜੀਟੇਟਿਡ ਕੈਪੇਸੀਟਰਾਂ ਦੁਆਰਾ ਬਦਲਿਆ ਜਾ ਸਕਦਾ ਹੈ, ਜੋ ਕਿ ਵਪਾਰਕ ਇਲੈਕਟ੍ਰਾਨਿਕ ਡਿਜ਼ਾਈਨ ਆਟੋਮੇਸ਼ਨ ਟੂਲਸ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਸਿੰਥੇਸਾਈਜ਼ ਕੀਤੇ ਜਾਂਦੇ ਹਨ। ਹੋਰ ਰਿਪੋਰਟ ਕੀਤੇ ਗਏ ਬ੍ਰੌਡਬੈਂਡ ਰੈਕਟੇਨਾ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਇਨਪੁਟ 'ਤੇ ਇੱਕ RF ਸ਼ਾਰਟ ਬਣਾਉਣ ਲਈ ਘੱਟ ਫ੍ਰੀਕੁਐਂਸੀ ਅਤੇ ਵੰਡੀਆਂ ਗਈਆਂ ਐਲੀਮੈਂਟਸ ਨਾਲ ਮੇਲ ਕਰਨ ਲਈ ਲੰਪਡ ਐਲੀਮੈਂਟਸ ਨੂੰ ਜੋੜਦੇ ਹਨ।

ਇੱਕ ਸਰੋਤ (ਜਿਸਨੂੰ ਸਰੋਤ-ਖਿੱਚ ਤਕਨੀਕ ਕਿਹਾ ਜਾਂਦਾ ਹੈ) ਰਾਹੀਂ ਲੋਡ ਦੁਆਰਾ ਦੇਖੇ ਗਏ ਇਨਪੁਟ ਇਮਪੀਡੈਂਸ ਨੂੰ ਬਦਲਣ ਦੀ ਵਰਤੋਂ 57% ਸਾਪੇਖਿਕ ਬੈਂਡਵਿਡਥ (1.25–2.25 GHz) ਅਤੇ ਲੰਪਡ ਜਾਂ ਡਿਸਟ੍ਰੀਬਿਊਟਡ ਸਰਕਟਾਂ ਦੇ ਮੁਕਾਬਲੇ 10% ਵੱਧ PCE ਵਾਲੇ ਬ੍ਰੌਡਬੈਂਡ ਰੀਕਟੀਫਾਇਰ ਨੂੰ ਡਿਜ਼ਾਈਨ ਕਰਨ ਲਈ ਕੀਤੀ ਗਈ ਹੈ। ਹਾਲਾਂਕਿ ਮੇਲ ਖਾਂਦੇ ਨੈੱਟਵਰਕ ਆਮ ਤੌਰ 'ਤੇ ਪੂਰੇ 50Ω ਬੈਂਡਵਿਡਥ 'ਤੇ ਐਂਟੀਨਾ ਨਾਲ ਮੇਲ ਕਰਨ ਲਈ ਤਿਆਰ ਕੀਤੇ ਜਾਂਦੇ ਹਨ, ਸਾਹਿਤ ਵਿੱਚ ਅਜਿਹੀਆਂ ਰਿਪੋਰਟਾਂ ਹਨ ਜਿੱਥੇ ਬ੍ਰੌਡਬੈਂਡ ਐਂਟੀਨਾ ਨੂੰ ਨੈਰੋਬੈਂਡ ਰੀਕਟੀਫਾਇਰ ਨਾਲ ਜੋੜਿਆ ਗਿਆ ਹੈ।

ਹਾਈਬ੍ਰਿਡ ਲੁੰਪਡ-ਐਲੀਮੈਂਟ ਅਤੇ ਡਿਸਟ੍ਰੀਬਿਊਟਡ-ਐਲੀਮੈਂਟ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਟੌਪੋਲੋਜੀ C ਅਤੇ D ਵਿੱਚ ਵਿਆਪਕ ਤੌਰ 'ਤੇ ਵਰਤੇ ਗਏ ਹਨ, ਜਿਸ ਵਿੱਚ ਸੀਰੀਜ਼ ਇੰਡਕਟਰ ਅਤੇ ਕੈਪੇਸੀਟਰ ਸਭ ਤੋਂ ਵੱਧ ਵਰਤੇ ਜਾਣ ਵਾਲੇ ਲੁੰਪਡ ਐਲੀਮੈਂਟ ਹਨ। ਇਹ ਗੁੰਝਲਦਾਰ ਬਣਤਰਾਂ ਜਿਵੇਂ ਕਿ ਇੰਟਰਡਿਜੀਟੇਟਿਡ ਕੈਪੇਸੀਟਰਾਂ ਤੋਂ ਬਚਦੇ ਹਨ, ਜਿਨ੍ਹਾਂ ਲਈ ਮਿਆਰੀ ਮਾਈਕ੍ਰੋਸਟ੍ਰਿਪ ਲਾਈਨਾਂ ਨਾਲੋਂ ਵਧੇਰੇ ਸਹੀ ਮਾਡਲਿੰਗ ਅਤੇ ਫੈਬਰੀਕੇਸ਼ਨ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ।

ਡਾਇਓਡ ਦੀ ਗੈਰ-ਰੇਖਿਕਤਾ ਦੇ ਕਾਰਨ, ਰੀਕਟੀਫਾਇਰ ਨੂੰ ਇਨਪੁਟ ਪਾਵਰ ਇਨਪੁਟ ਇਮਪੀਡੈਂਸ ਨੂੰ ਪ੍ਰਭਾਵਿਤ ਕਰਦਾ ਹੈ। ਇਸ ਲਈ, ਰੈਕਟੇਨਾ ਨੂੰ ਇੱਕ ਖਾਸ ਇਨਪੁਟ ਪਾਵਰ ਪੱਧਰ ਅਤੇ ਲੋਡ ਇਮਪੀਡੈਂਸ ਲਈ PCE ਨੂੰ ਵੱਧ ਤੋਂ ਵੱਧ ਕਰਨ ਲਈ ਤਿਆਰ ਕੀਤਾ ਗਿਆ ਹੈ। ਕਿਉਂਕਿ ਡਾਇਓਡ ਮੁੱਖ ਤੌਰ 'ਤੇ 3 GHz ਤੋਂ ਘੱਟ ਫ੍ਰੀਕੁਐਂਸੀ 'ਤੇ ਕੈਪੇਸਿਟਿਵ ਉੱਚ ਇਮਪੀਡੈਂਸ ਹੁੰਦੇ ਹਨ, ਬ੍ਰੌਡਬੈਂਡ ਰੈਕਟੇਨਾ ਜੋ ਮੇਲ ਖਾਂਦੇ ਨੈੱਟਵਰਕਾਂ ਨੂੰ ਖਤਮ ਕਰਦੇ ਹਨ ਜਾਂ ਸਰਲੀਕ੍ਰਿਤ ਮੈਚਿੰਗ ਸਰਕਟਾਂ ਨੂੰ ਘੱਟ ਤੋਂ ਘੱਟ ਕਰਦੇ ਹਨ, ਫ੍ਰੀਕੁਐਂਸੀ Prf>0 dBm ਅਤੇ 1 GHz ਤੋਂ ਉੱਪਰ 'ਤੇ ਕੇਂਦ੍ਰਿਤ ਕੀਤੇ ਗਏ ਹਨ, ਕਿਉਂਕਿ ਡਾਇਓਡਾਂ ਵਿੱਚ ਘੱਟ ਕੈਪੇਸਿਟਿਵ ਇਮਪੀਡੈਂਸ ਹੁੰਦਾ ਹੈ ਅਤੇ ਐਂਟੀਨਾ ਨਾਲ ਚੰਗੀ ਤਰ੍ਹਾਂ ਮੇਲ ਖਾਂਦਾ ਹੈ, ਇਸ ਤਰ੍ਹਾਂ ਇਨਪੁਟ ਰਿਐਕਟੈਂਸ >1,000Ω ਵਾਲੇ ਐਂਟੀਨਾ ਦੇ ਡਿਜ਼ਾਈਨ ਤੋਂ ਬਚਿਆ ਜਾ ਸਕਦਾ ਹੈ।

CMOS ਰੈਕਟੇਨਾ ਵਿੱਚ ਅਨੁਕੂਲ ਜਾਂ ਮੁੜ-ਸੰਰਚਿਤ ਇਮਪੀਡੈਂਸ ਮੈਚਿੰਗ ਦੇਖੀ ਗਈ ਹੈ, ਜਿੱਥੇ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਵਿੱਚ ਔਨ-ਚਿੱਪ ਕੈਪੇਸੀਟਰ ਬੈਂਕ ਅਤੇ ਇੰਡਕਟਰ ਹੁੰਦੇ ਹਨ। ਸਟੈਂਡਰਡ 50Ω ਐਂਟੀਨਾ ਦੇ ਨਾਲ-ਨਾਲ ਸਹਿ-ਡਿਜ਼ਾਈਨ ਕੀਤੇ ਲੂਪ ਐਂਟੀਨਾ ਲਈ ਸਟੈਟਿਕ CMOS ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਵੀ ਪ੍ਰਸਤਾਵਿਤ ਕੀਤੇ ਗਏ ਹਨ। ਇਹ ਰਿਪੋਰਟ ਕੀਤਾ ਗਿਆ ਹੈ ਕਿ ਪੈਸਿਵ CMOS ਪਾਵਰ ਡਿਟੈਕਟਰ ਉਹਨਾਂ ਸਵਿੱਚਾਂ ਨੂੰ ਨਿਯੰਤਰਿਤ ਕਰਨ ਲਈ ਵਰਤੇ ਜਾਂਦੇ ਹਨ ਜੋ ਐਂਟੀਨਾ ਦੇ ਆਉਟਪੁੱਟ ਨੂੰ ਉਪਲਬਧ ਪਾਵਰ ਦੇ ਅਧਾਰ ਤੇ ਵੱਖ-ਵੱਖ ਰੀਕਟੀਫਾਇਰ ਅਤੇ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕਾਂ ਵੱਲ ਨਿਰਦੇਸ਼ਤ ਕਰਦੇ ਹਨ। ਲੁੰਪਡ ਟਿਊਨੇਬਲ ਕੈਪੇਸੀਟਰਾਂ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹੋਏ ਇੱਕ ਮੁੜ-ਸੰਰਚਿਤ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕ ਦਾ ਪ੍ਰਸਤਾਵ ਰੱਖਿਆ ਗਿਆ ਹੈ, ਜੋ ਕਿ ਵੈਕਟਰ ਨੈੱਟਵਰਕ ਵਿਸ਼ਲੇਸ਼ਕ ਦੀ ਵਰਤੋਂ ਕਰਕੇ ਇਨਪੁੱਟ ਇਮਪੀਡੈਂਸ ਨੂੰ ਮਾਪਦੇ ਹੋਏ ਫਾਈਨ-ਟਿਊਨਿੰਗ ਦੁਆਰਾ ਟਿਊਨ ਕੀਤਾ ਜਾਂਦਾ ਹੈ। ਮੁੜ-ਸੰਰਚਿਤ ਮਾਈਕ੍ਰੋਸਟ੍ਰਿਪ ਮੈਚਿੰਗ ਨੈੱਟਵਰਕਾਂ ਵਿੱਚ, ਡੁਅਲ-ਬੈਂਡ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਨੂੰ ਪ੍ਰਾਪਤ ਕਰਨ ਲਈ ਮੈਚਿੰਗ ਸਟੱਬਾਂ ਨੂੰ ਅਨੁਕੂਲ ਕਰਨ ਲਈ ਫੀਲਡ ਇਫੈਕਟ ਟਰਾਂਜ਼ਿਸਟਰ ਸਵਿੱਚਾਂ ਦੀ ਵਰਤੋਂ ਕੀਤੀ ਗਈ ਹੈ।

ਐਂਟੀਨਾ ਬਾਰੇ ਹੋਰ ਜਾਣਨ ਲਈ, ਕਿਰਪਾ ਕਰਕੇ ਇੱਥੇ ਜਾਓ:

ਪੋਸਟ ਸਮਾਂ: ਅਗਸਤ-09-2024